Intel Agilex Logic Array Blocks og Adaptive Logic Modules

Intel® Agilex™ LAB og ALM Overview

Rökfylkisblokkin (LAB) er samsett úr grunnbyggingareiningum sem kallast aðlagandi rökfræðieiningar (ALM). Þú getur stillt rannsóknarstofur til að innleiða rökfræðiaðgerðir, reikniaðgerðir og skráningaraðgerðir.

Þú getur notað helming af tiltækum LABs í Intel® Agilex™ tækjunum sem minni LABs (MLABs). Sum tæki kunna að hafa hærra MLAB hlutfall.

Intel Quartus® Prime hugbúnaðurinn og önnur studd smíðaverkfæri þriðja aðila velja sjálfkrafa viðeigandi stillingu fyrir algengar aðgerðir eins og teljara, samanlagt, frádrátt og reikniaðgerðir.

Intel Hyperflex™ kjarnaarkitektúr, Intel Agilex tæki yfirview

Veitir frekari upplýsingar um Hyper-Registers og Intel Hyperflex™ kjarnaarkitektúr. Hyper-Registers eru viðbótarskrár sem eru fáanlegar í öllum samtengingarleiðarhlutum í gegnum kjarnaefnið, þar með talið leiðarhlutana sem eru tengdir við LAB inntak og úttak.

Intel Hyperflex™ skráning

Intel Agilex tækjafjölskyldan er byggð á Intel Hyperflex™ kjarnaarkitektúr.

Intel Agilex LAB inniheldur Intel Hyperflex skrár og aðra eiginleika sem eru hannaðir til að auðvelda endurtímasetningu. Intel Hyperflex skrár eru fáanlegar í ALM og burðarkeðjum. Eins og sýnt er á myndinni um Intel Agilex ALM Connection Details, eru Intel Hyperflex skrárnar staðsettar á samstilltu tærinu og klukka gerir inntak kleift að auka eða draga úr seinkun á slóð. Hægt er að virkja allar Intel Hyperflex skrárnar og þær eru stjórnaðar af Intel Quartus Prime hugbúnaðinum meðan á endurtímasetningu stendur.

Intel Agilex LAB og ALM arkitektúr og eiginleikar

Eftirfarandi hlutar lýsa LAB og ALM fyrir Intel Agilex tæki.

LAB

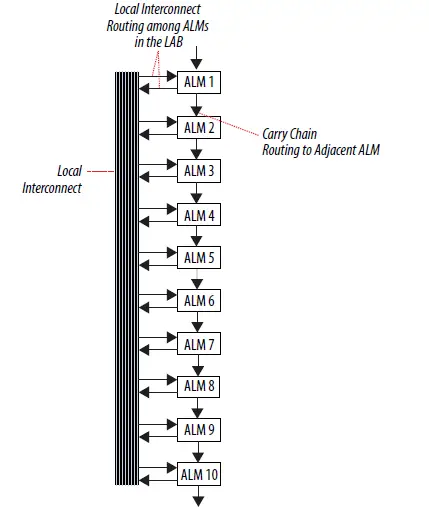

LABs eru stillanlegar rökfræðiblokkir sem samanstanda af hópi rökfræðilegra auðlinda. Hvert rannsóknarstofu inniheldur sérstaka rökfræði til að keyra stjórnmerki til ALMs þess. MLAB er ofursett af LAB og inniheldur alla LAB eiginleika. Það eru samtals 10 ALM í hverju rannsóknarstofu, eins og sýnt er á Intel Agilex LAB og MLAB uppbyggingu myndinni.

Mynd 1.

Intel Agilex LAB uppbygging og samtengingar yfirview

Þessi mynd sýnir yfirview af Intel Agilex LAB og MLAB uppbyggingunni með LAB samtengunum.

Tengdar upplýsingar

Tengdar upplýsingar

MLAB á síðu 6

MLAB

Hver MLAB styður að hámarki 640 bita af einföldu SRAM með tvöföldum tengi. Þú getur stillt hverja ALM í MLAB sem 32 (dýpt) x 2 (breidd) minnisblokk, sem leiðir til uppsetningar á 32 (dýpt) x 20 (breidd) einföldum tvítengja SRAM blokk.

Mynd 2.

Intel Agilex LAB og MLAB uppbygging Staðbundin og bein tengitenging

Staðbundin og bein tengitenging

Hvert LAB getur keyrt út 60 ALM úttak. Hlutmengi þessara getur beint LAB inntak, en allar tengingar við aðra röð eða dálk verða að nota að minnsta kosti einn almennan leiðarvír.

Staðbundin samtenging rekur ALM inntak. ALM úttak, sem og dálka- og raðtengingar knýja staðbundna samtenginguna.

Mynd 3. Intel Agilex LAB staðbundin og bein tengitenging  Carry Chain samtengi

Carry Chain samtengi

Það er sérstök burðarkeðjuleið á milli ALMs. Intel Agilex tæki innihalda aukna samtengingarbyggingu í Labs til að beina burðarkeðjum fyrir skilvirkar reikniaðgerðir. Þessar ALM-til-ALM tengingar fara framhjá staðbundnu samtengingunni.

Intel Hyperflex skránum er bætt við burðarkeðjuna til að gera sveigjanlega endurtímasetningu yfir keðju rannsóknarstofnana og Intel Quartus Prime þýðandinn nýtur sjálfkrafatage af þessum auðlindum til að bæta nýtingu og afköst.

Mynd 4. Carry Chain samtengi LAB stýrimerki

LAB stýrimerki

Það eru tveir klukkugjafar í hverri LAB stjórnblokk, sem mynda tvær LAB klukkur (LABCLK[1:0]) og tvær seinkaðar LAB klukkur (LABCLK_Phi1[1:0]) til að keyra ALM skrárnar og Hyper-Registers í LAB. LAB styður tvö einstök klukkuvirkjunarmerki, sem og fleiri skýr merki, fyrir ALM skrárnar.

LAB raðklukkurnar [5..0] og LAB staðbundnar samtengingar búa til stjórnmerkin um allt LAB. Lítið skekkt klukkanet dreifir alþjóðlegum merkjum til raðklukkanna [5..0]. MultiTrack samtengingin samanstendur af samfelldum, afkasta-bjartsýni leiðarlínum af mismunandi lengd og hraða sem notaðar eru til skilvirkni leiðar. Intel Quartus Prime þýðandinn beinir sjálfkrafa mikilvægum hönnunarleiðum á hraðari samtengdum til að bæta hönnunarafköst og hámarka auðlindir tækisins.

Clear Logic Control

Merki um allt LAB stjórna rökfræðinni fyrir skýrt merki ALM skrárinnar. ALM skráin styður beint bæði samstillt og ósamstillt hreinsun. Hvert LAB styður eitt samstillt hreint merki og tvö ósamstillt skýr merki.

Intel Agilex tæki bjóða upp á endurstillingarpinna fyrir allan tækjabúnað (DEV_CLRn) sem endurstillir allar skrár í tækinu. Þú getur virkjað DEV_CLRn pinna í Intel Quartus Prime hugbúnaðinum fyrir samantekt. Endurstillingarmerki alls tækisins hnekkir öllum öðrum stýrimerkjum.

Mynd 5. Intel Agilex LAB-Wide stýrimerki

ALM

Eftirfarandi hlutar fjalla um ALM tilföng, ALM úttak og ALM rekstrarham.

ALM auðlindir

Hver ALM inniheldur margs konar LUT-undirstaða tilföng sem hægt er að skipta á milli tveggja samsettra aðlögunar LUT (ALUT), tveggja bita fullan samanleggjara og fjögurra skráa.

Með allt að átta inntakum fyrir tvö samsett ALUT getur einn ALM útfært ýmsar samsetningar tveggja aðgerða. Þessi aðlögunarhæfni gerir ALM kleift að vera algjörlega afturábak-samhæft við fjögur inntak LUT arkitektúra. Eitt ALM getur einnig útfært undirmengi átta inntaksaðgerða.

Ein ALM inniheldur fjórar forritanlegar skrár. Hver skrá hefur eftirfarandi höfn:

- Gögn í

- Gögn út

- Venjuleg LAB klukka

- Seinkuð LAB klukka

- Klukka virkja

- Samstilltur skýr

- Ósamstilltur skýr

Alþjóðleg merki, almennar I/O (GPIO) pinnar, eða hvaða innri rökfræði sem er, geta knúið klukkuna til að virkja merki, klukku og ósamstillt eða samstillt hreinsunarmerki ALM skráar. Klukkuvirkjamerkið hefur forgang fram yfir samstillt endurstillingarmerki.

Fyrir samsettar aðgerðir er farið framhjá skránum og úttak uppflettitöflunnar (LUT) og samanleggjara keyrir beint á úttak ALM. Tveir hraðvirkir útgangar eru fáanlegir fyrir 6 LUT úttak og neðstu 5 LUT úttak til að komast framhjá úttaksmux og tengja við annað LAB fyrir mikilvæga leiðstillingu.

Mynd 6. Intel Agilex ALM háþróaður blokkamynd

ALM úttak

ALM úttak

Almenn leiðarúttak í hverju ALM rekur staðbundið, línu- og dálkaleiðartilföng. Sex ALM úttak, þar á meðal tvær hraðvirkar úttaksleiðir, geta keyrt dálka-, röð- eða beinleiðartengingar.

LUT, adder, eða register framleiðsla getur keyrt ALM úttakið. Bæði LUT eða adder og ALM skrá geta ekið út úr ALM samtímis.

Skráapökkun bætir nýtingu tækja með því að leyfa ótengdri skrá og samsettri rökfræði að vera pakkað inn í eina ALM. ALM getur einnig keyrt út skráðar og óskráðar útgáfur af LUT eða adder úttakinu.

Eftirfarandi mynd sýnir Intel Agilex ALM tenginguna. Í Intel Quartus Prime Resource Property Editor er öll ALM tengingin einfölduð. Sumar leiðir verða fluttar innbyrðis með Intel Quartus Prime hugbúnaðinum.

Mynd 7. Intel Agilex ALM tengingarupplýsingar ALM rekstrarhamur

ALM rekstrarhamur

Intel Agilex ALM virkar í einhverjum af eftirfarandi stillingum:

- Venjulegur háttur

- Lengri LUT ham

- Reiknihamur

Venjulegur háttur

Venjulegur háttur gerir kleift að útfæra tvær aðgerðir í einni Intel Agilex ALM, eða einni aðgerð með allt að sex inntakum.

Allt að átta gagnainntak frá LAB staðbundinni samtengingu eru inntak til samsetningarrökfræðinnar.

ALM getur stutt ákveðnar samsetningar af algjörlega sjálfstæðum aðgerðum og ýmsum samsetningum aðgerða sem hafa sameiginleg inntak.

Intel Quartus Prime Compiler velur sjálfkrafa inntak til LUT. ALM í venjulegum ham styðja skráapökkun.

Eftirfarandi mynd sýnir blöndu af mismunandi inntakstengingum fyrir LUT stillinguna. Í hönnun þinni gæti Intel Quartus Prime hugbúnaðurinn úthlutað mismunandi inntaksnöfnum við söfnun.

Mynd 8. ALM í venjulegum ham

Samsetningar aðgerða með færri inntak en þær sem sýndar eru eru einnig studdar. Til dæmisample, samsetningar aðgerða með eftirfarandi fjölda inntaks eru studdar.

- 4 og 3

- 3 og 3

- 3 og 2

- 5 og 2

Til að pakka tveimur 5-inntaksaðgerðum í eitt ALM, verða aðgerðir að hafa að minnsta kosti tvö sameiginleg inntak. Algeng inntak eru dataa og datab. Samsetning 4-inntaksaðgerðar og 5-inntaksaðgerðar krefst eins sameiginlegs inntaks (annaðhvort dataa eða datab).

Í fátæku tæki er hægt að útfæra aðgerðir sem hægt væri að setja í eina ALM í aðskildum ALM með Intel Quartus Prime hugbúnaðinum til að ná sem bestum árangri. Þegar tæki byrjar að fyllast nýtir Intel Quartus Prime hugbúnaðurinn sjálfkrafa alla möguleika Intel Agilex ALM. Intel Quartus Prime Compiler leitar sjálfkrafa að aðgerðum með algengum inntakum eða algjörlega sjálfstæðum aðgerðum til að setja í eina ALM til að nýta auðlindir tækisins á skilvirkan hátt. Að auki geturðu stjórnað auðlindanotkun handvirkt með því að stilla staðsetningarúthlutun.

Mynd 9. 6-inntak LUT-hamur í venjulegri stillingu

Mynd 10. 3-inntak LUT-hamur í venjulegri stillingu

Mynd 10. 3-inntak LUT-hamur í venjulegri stillingu

gögn og gögn b eru tiltæk fyrir skráarpökkun.  Þú getur innleitt hvaða þriggja til sex inntaksaðgerð sem er með því að nota eftirfarandi inntak:

Þú getur innleitt hvaða þriggja til sex inntaksaðgerð sem er með því að nota eftirfarandi inntak:

- datae

- datad0

- datac0

- datac1

- datad1

- dataf

- gögn og gögn — þar sem gögnum og gögnum er deilt á báðar LUT til að veita sveigjanleika til að innleiða mismunandi aðgerð í hverjum LUT.

Bæði gagna- og gagnainntak styðja skráapökkunareiginleikann. Ef þú kveikir á skráapökkunareiginleikanum, fara bæði gagna- og gagnainntak eða annaðhvort inntak framhjá LUT og beint inn í skrána, allt eftir pakkaðri skráarstillingu sem notuð er. Fyrir Intel Agilex tæki eru eftirfarandi gerðir af pakkaðri skráarstillingum studdar:

- 5-inntak LUT með 1 pakkaðri skráarleið

- 5-inntak LUT með 2 pakkaðri skráarleiðum

- Tvær 3-inntak LUTs með 2 pakkaðar skráarleiðir

3-inntak LUT með 2 pakkaðri skráarleiðum er sýnd á myndinni 3-inntak LUT Mode Function í Normal Mode. Fyrir Intel Agilex tæki styður 6-inntak LUT stillingin ekki skráarpökkunareiginleikann.

Lengri LUT-stilling

Mynd 11. Studdar 8-inntaksaðgerðir í útbreiddri LUT ham

Hægt er að útfæra ákveðnar 8 inntaksaðgerðir í einni ALM með því að nota öll LUT inntak:

- datae

- datad0

- datac0

- dataa

- gagnabanka

- datac1

- datad1

- dataf

Í 8-inntak auknu LUT-hamnum er pakkað skráarhamur studdur, að því tilskildu að pakkaða skráin deili gagna- eða gagnainntaki með 8-inntaks LUT.

Reiknihamur

ALM í reikningsham notar tvö sett af tveimur 4-inntak LUTs ásamt tveimur sérstökum fullum upptökum. Sérsniðnu adderarnir gera LUT-tækjunum kleift að framkvæma for-adder rökfræði. Þess vegna getur hver addari bætt við framleiðslu tveggja 4-inntaksaðgerða.

Reiknistilling býður einnig upp á klukkuvirkjun, teljaravirkja, samstillta upp og niður stjórn, bæta við og draga frá stjórn og samstillt hreinsa.

Hreinsuðu og klukkuvirku valkostirnir eru merki um allt LAB sem hafa áhrif á allar skrár í LAB. Þú getur slökkt á eða virkjað þessi merki fyrir sig fyrir hvert par af skrám í aðlögunarhæfni LUT (ALUT). Intel Quartus Prime hugbúnaðurinn setur sjálfkrafa allar skrár sem teljarinn notar ekki í önnur rannsóknarstofur.

Mynd 12. Intel Agilex ALM í reikniham

Burðarkeðja

Burðarkeðja

Burðarkeðjan veitir hraðvirka burðaraðgerð á milli sérstakra uppbótar í reikniham.

2-bita burðarvalseiginleikinn í Intel Agilex tækjum skiptir útbreiðslu seinkun burðarkeðja með ALM. Burðarkeðjur geta byrjað annað hvort í fyrsta ALM eða sjötta ALM í rannsóknarstofu. Lokaútfærslumerkinu er beint til ALM, þar sem það er fært til staðbundinna, línu- eða dálkatenginga.

Endurskoðunarsaga skjala fyrir Intel Agilex Logic Array Blocks og Adaptive Logic Modules User Guide

| Skjalaútgáfa | Breytingar |

| 2022.05.24 | Uppfærð mynd: Intel Agilex ALM blokkamynd á háu stigi. |

| 2019.11.14 | Uppfærði lýsinguna í LAB Control Signals hlutanum. |

| 2019.10.01 |

|

| 2019.04.02 | Upphafleg útgáfa. |

Intel Corporation.

Allur réttur áskilinn. Intel, Intel lógóið og önnur Intel merki eru vörumerki Intel Corporation eða dótturfélaga þess. Intel ábyrgist frammistöðu FPGA- og hálfleiðaravara sinna samkvæmt gildandi forskriftum í samræmi við staðlaða ábyrgð Intel, en áskilur sér rétt til að gera breytingar á hvaða vörum og þjónustu sem er hvenær sem er án fyrirvara. Intel tekur enga ábyrgð eða ábyrgð sem stafar af notkun eða notkun á neinum upplýsingum, vöru eða þjónustu sem lýst er hér nema sérstaklega hafi verið samið skriflega af Intel. Viðskiptavinum Intel er bent á að fá nýjustu útgáfuna af tækjaforskriftum áður en þeir treysta á birtar upplýsingar og áður en þeir panta vörur eða þjónustu.

*Önnur nöfn og vörumerki geta verið eign annarra.

ISO

9001:2015

Skráður

Skjöl / auðlindir

|

Intel Agilex Logic Array Blocks og Adaptive Logic Modules [pdfNotendahandbók Agilex Logic Array Blocks og Adaptive Logic Modules, Agilex, Logic Array Blocks og Adaptive Logic Modules, Array Blocks og Adaptive Logic Modules, Adaptive Logic Modules, Logic Modules |