Intel High-Level Synthesis Compiler Pro Edition

Upplýsingar um vöru

| Vöruheiti | Intel High-Level Synthesis Compiler Pro Edition |

|---|---|

| Útgáfa | 22.4 |

| Útgáfudagur | 19. desember 2022 |

| Úrsagnartilkynning | Fyrirhugað er að Intel High-Level Synthesis Compiler verði úrelt eftir útgáfu 23.4. |

Notkunarleiðbeiningar fyrir vöru

Leiðbeiningar um að byrja

- Frumstilltu þýðandaumhverfið þitt.

- Review hin ýmsu hönnun tdamples og kennsluefni sem fylgja með Intel HLS þýðandanum.

Notendahandbók

- Notendahandbókin veitir leiðbeiningar um

- Að búa til, sannreyna og líkja eftir hugverkarétti (IP) hannað fyrir Intel FPGA vörur.

- Að fara í gegnum allt þróunarflæði íhlutarins þíns frá því að búa til íhlutinn þinn og prófunarbekkinn þinn upp í að samþætta IP-íhlutann þinn í stærra kerfi með Intel Quartus Prime hugbúnaðinum.

Leiðbeiningar um bestu starfsvenjur

Leiðbeiningar um bestu starfsvenjur veitir tækni og starfshætti sem þú getur beitt til að bæta FPGA svæðisnýtingu og afköst HLS íhlutsins. Notaðu þessar bestu starfsvenjur eftir að hafa staðfest virkni íhlutans.

Tilvísunarhandbók

Tilvísunarhandbókin veitir tilvísunarupplýsingar um eiginleikana sem Intel HLS þýðandinn styður. Finndu upplýsingar um Intel HLS Compiler skipanavalkosti, haus files, pragmas, eiginleikar, fjölvi, yfirlýsingar, rök og sniðmátssöfn.

Intel® High Level Synthesis Compiler Pro Edition útgáfu 22.4 útgáfuskýringar

- Intel® High Level Synthesis Compiler Pro Edition útgáfuskýrslur veita síðbúnar upplýsingar um Intel High Level Synthesis Compiler Pro Edition útgáfu 22.4.

Beðið er afnám Intel HLS þýðanda

- Til að halda aðgangi að nýjustu FPGA hágæða hönnunareiginleikum, hagræðingu og þróunartólum skaltu flytja núverandi hönnun þína til að nota Intel oneAPI Base Toolkit.

- Áætlað er að Intel High Level Synthesis (HLS) þýðandinn verði úreltur eftir útgáfu 23.4.

- Farðu á Intel oneAPI vörusíðuna til að fá ráðleggingar um flutning, eða farðu á Intel High Level Design samfélagsvettvanginn fyrir allar spurningar eða beiðnir.

Um Intel HLS Compiler Pro Edition Documentation Library

- Skjöl fyrir Intel HLS Compiler Pro Edition er skipt í nokkur rit. Notaðu eftirfarandi töflu til að finna útgáfuna sem inniheldur Intel HLS Compiler Pro Edition upplýsingarnar sem þú ert að leita að:

Tafla 1. Intel High-Level Synthesis Compiler Pro Edition Documentation Library

| Titill og lýsing | |

| Útgáfuskýringar

Veitir nýjar upplýsingar um Intel HLS þýðanda. |

Tengill |

| Leiðbeiningar um að byrja

Komdu í gang með Intel HLS þýðandanum með því að læra hvernig á að frumstilla þýðandaumhverfið þitt og endurstillaviewí hinni ýmsu hönnun tdamples og kennsluefni sem fylgja með Intel HLS þýðandanum. |

Tengill |

| Notendahandbók

Veitir leiðbeiningar um að búa til, sannreyna og líkja eftir hugverkarétti (IP) sem þú hannar fyrir Intel FPGA vörur. Farðu í gegnum allt þróunarflæði íhlutarins þíns, frá því að búa til íhlutinn þinn og prófunarbekkinn upp að því að samþætta IP-tölu íhluta þinnar í stærra kerfi með Intel Quartus Prime hugbúnaðinum. |

Tengill |

| Leiðbeiningar um bestu starfsvenjur

Veitir tækni og venjur sem þú getur beitt til að bæta FPGA svæðisnýtingu og afköst HLS íhlutsins þíns. Venjulega beitir þú þessum bestu starfsvenjum eftir að þú hefur staðfest virkni íhlutsins þíns. |

Tengill |

| Tilvísunarhandbók

Veitir tilvísunarupplýsingar um þá eiginleika sem Intel HLS þýðandinn styður. Finndu upplýsingar um Intel HLS Compiler skipanavalkosti, haus files, pragmas, eiginleikar, fjölvi, yfirlýsingar, rök og sniðmátssöfn. |

Tengill |

Intel Corporation. Allur réttur áskilinn. Intel, Intel lógóið og önnur Intel merki eru vörumerki Intel Corporation eða dótturfélaga þess. Intel ábyrgist frammistöðu FPGA- og hálfleiðaravara sinna samkvæmt gildandi forskriftum í samræmi við staðlaða ábyrgð Intel, en áskilur sér rétt til að gera breytingar á hvaða vörum og þjónustu sem er hvenær sem er án fyrirvara. Intel tekur enga ábyrgð eða skaðabótaábyrgð sem stafar af notkun eða notkun á neinum upplýsingum, vöru eða þjónustu sem lýst er hér nema sérstaklega hafi verið samið skriflega af Intel. Viðskiptavinum Intel er bent á að fá nýjustu útgáfuna af tækjaforskriftum áður en þeir treysta á birtar upplýsingar og áður en pantað er fyrir vörur eða þjónustu.

*Önnur nöfn og vörumerki geta verið eign annarra.

Beðið er afnám Intel HLS þýðanda

- Til að halda aðgangi að nýjustu FPGA hágæða hönnunareiginleikum, hagræðingu og þróunartólum skaltu flytja núverandi hönnun þína til að nota Intel oneAPI Base Toolkit.

- Áætlað er að Intel High Level Synthesis (HLS) þýðandinn verði úreltur eftir útgáfu 23.4.

- Farðu á Intel oneAPI vörusíðuna til að fá ráðleggingar um flutning, eða farðu á Intel High Level Design samfélagsvettvanginn fyrir allar spurningar eða beiðnir.

Nýir eiginleikar og endurbætur

- Intel High Level Synthesis Compiler Pro Edition útgáfa 22.4 inniheldur eftirfarandi nýja eiginleika:

- Viðhaldsútgáfa.

- Engir nýir eiginleikar eða endurbætur fyrir Intel HLS Compiler Pro Edition útgáfu 22.4.

Breytingar á hegðun hugbúnaðar

- Þessi hluti skráir tilvik þar sem eiginleikar Intel HLS Compiler Pro Edition útgáfa 22.4 hafa breyst frá fyrri útgáfum þýðandans.

Viðhaldsútgáfa.

- Engar breytingar á hegðun hugbúnaðar fyrir Intel HLS Compiler Pro Edition útgáfu 22.4.

Forsendur Intel High-Level Synthesis Compiler Pro Edition

- Intel HLS Compiler Pro Edition er hluti af Intel Quartus® Prime Pro Edition Design Suite. Þú getur sett upp Intel HLS þýðanda sem hluta af Intel Quartus Prime hugbúnaðaruppsetningunni þinni eða sett hann upp sérstaklega. Það þarf Intel Quartus Prime og viðbótarhugbúnað til að nota.

- Fyrir nákvæmar leiðbeiningar um uppsetningu Intel Quartus Prime Pro Edition hugbúnaðar, þar á meðal kerfiskröfur, forsendur og leyfiskröfur, sjá Intel FPGA hugbúnaðaruppsetningu og leyfisveitingu.

- Intel HLS þýðandinn krefst eftirfarandi hugbúnaðar til viðbótar við Intel Quartus Prime:

C++ þýðanda

- Í Linux þarf Intel HLS þýðanda GCC 9.3.0 þar á meðal GNU C++ bókasafnið og tvöfalda tól (binutils).

- Þessi útgáfa af GCC er veitt sem hluti af Intel HLS þýðandauppsetningunni þinni. Eftir uppsetningu Intel HLS þýðanda er GCC 9.3.0 fáanlegt í /gcc.

- Mikilvægt: Intel HLS þýðandinn notar /gcc skrá sem verkfærakeðjuskrá hennar. Notaðu þessa uppsetningu á GCC fyrir alla HLS-tengda hönnunarvinnu þína.

- Fyrir Windows skaltu setja upp eina af eftirfarandi útgáfum af Microsoft* Visual Studio* Professional:

- Microsoft Visual Studio 2017 Professional

- Microsoft Visual Studio 2017 samfélag

- Til að fá nýjustu C++17 stuðninginn skaltu ganga úr skugga um að þú sért að nota nýjustu útgáfuna af Visual Studio 2017.

- Mikilvægt: Intel HLS þýðandahugbúnaðurinn styður ekki útgáfur af Microsoft Visual Studio aðrar en þær sem tilgreindar eru fyrir útgáfu hugbúnaðarins.

Siemens* EDA Questa® uppgerð hugbúnaður

- Á Windows og RedHat Linux kerfum geturðu sett upp Questa® uppgerð hugbúnaðinn frá Intel Quartus Prime hugbúnaðaruppsetningarforritinu. Valkostirnir sem eru í boði eru sem hér segir:

- Questa Intel FPGA útgáfa

- Questa Intel FPGA byrjendaútgáfa

- Bæði Questa Intel FPGA Edition og Questa Intel FPGA Starter Edition þurfa leyfi. Leyfið fyrir Questa Intel FPGA Starter Edition er ókeypis. Nánari upplýsingar er að finna í Intel FPGA hugbúnaðaruppsetningu og leyfisveitingu.

- Að öðrum kosti geturðu notað þína eigin leyfisútgáfu af Siemens* EDA ModelSim* SE eða Siemens EDA Questa Advanced Simulator hugbúnaðinum.

- Á Linux kerfum þurfa Questa – Intel FPGA Edition og Questa – Intel FPGA Starter Edition Red Hat* þróunarverkfærapakkana.

- Til að fá upplýsingar um allar ModelSim og Questa hugbúnaðarútgáfur sem Intel hugbúnaðurinn styður skaltu skoða hlutann EDA tengiupplýsingar í útgáfuskýringum hugbúnaðar og tækjastuðnings fyrir þína útgáfu af Intel Quartus Prime Pro Edition.

Tengdar upplýsingar

- Intel High Level Synthesis Compiler Byrjunarhandbók

- Styður stýrikerfi

- Hugbúnaðarkröfur í Intel FPGA hugbúnaðaruppsetningu og leyfisveitingu

- EDA tengiupplýsingar (Intel Quartus Prime Pro Edition)

Þekkt vandamál og lausnir

- Þessi hluti veitir upplýsingar um þekkt vandamál sem hafa áhrif á Intel HLS Compiler Pro Edition útgáfu 22.4.

| Lýsing | Lausn |

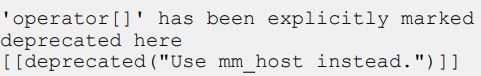

| Þegar þú notar úrelta bekkinn mm_master sendir þýðandinn frá sér viðvörunarskilaboð eins og eftirfarandi:

Þessi skilaboð gefa ekki til kynna hvaða hluta kóðans þíns þarf að breyta. |

Forðastu þessi viðvörunarskilaboð með því að nota bekkinn mm_host, sem kemur í staðinn fyrir úrelta bekkinn mm_master. |

| (Aðeins Windows) Samsetning hönnunar í möppu með löngu slóðarheiti getur leitt til misheppnaðar.

Athugaðu debug.log file fyrir „fann ekki file” villur. Þessar villur geta gefið til kynna að leiðin þín sé of löng. |

Settu hönnunina saman í möppu með stuttu nafni slóðar. |

| (Aðeins Windows) Löng leið fyrir Intel Quartus Prime uppsetningarskrána þína getur komið í veg fyrir að þú takist að setja saman og keyra Intel HLS Compiler kennsluefni og td.ample hönnun.

Athugaðu debug.log file fyrir „fann ekki file” villur. Þessar villur geta gefið til kynna að leiðin þín sé of löng. |

Færðu kennsluefnin og tdamples til stutts slóðarheits áður en reynt er að keyra þær. |

| Lýsing | Lausn |

| Bókasöfn sem miða á OpenCL* og eru skrifuð í HLS geta ekki notað strauma eða pípur sem viðmót á milli OpenCL kóða og bókasafnsins sem skrifað er í HLS.

Hins vegar getur bókasafnið í HLS notað strauma eða rör ef báðir endapunktar eru innan safnsins (td.ample, straumur sem tengir tvær verkefnisaðgerðir). |

N/A |

| Að nota ihc::maxburst færibreytuna á Avalon® Memory-Mapped hýsilviðmót getur valdið því að hönnunin þín hangir í uppgerð. | N/A |

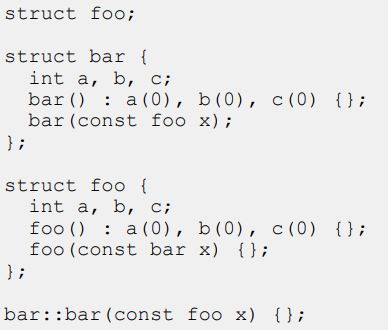

| Í sumum sjaldgæfum tilfellum, ef þú ert með tvo flokka þar sem smiðirnir krefjast tilvika af hinum bekknum sem inntak, gæti þýðandinn hrunið.

Til dæmisample, að setja saman eftirfarandi kóðabút veldur því að þýðandinn hrynur:

|

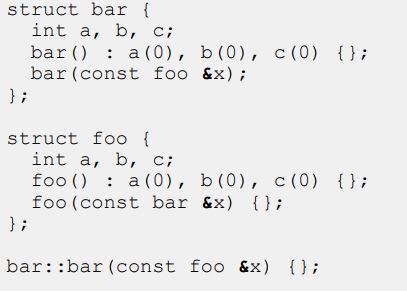

Forðastu að búa til hringlaga skilgreiningu. Í staðinn skaltu nota bendil eða tilvísun í afritunarsmiðinn þinn.

Til dæmisample, umbreyttu fyrri kóðabútinum í eftirfarandi kóða og sendu skipulagið sem tilvísun í smiðinn:

|

| Bókasöfn sem miða á OpenCL og eru skrifuð í HLS gætu valdið því að OpenCL kjarna sem innihalda bókasafnið hafi íhaldssamari stigvaxandi samantekt. | N/A |

| Þegar þú þróar bókasafn, ef þú ert með #define sem skilgreinir gildi sem þú notar síðar í #pragma, mistakast fpga_crossgen skipunin.

Til dæmisample, eftirfarandi kóða er ekki hægt að setja saman af

|

Notaðu pragma í stað #pragma.

Til dæmisample, eftirfarandi er sett saman með góðum árangri með

|

| Þegar þú notar -c skipanavalkostinn til að hafa aðskilda samantekt og tengingu stages í verkflæðinu þínu, og ef þú tilgreinir ekki -march valkostinn í tengiliðnumtage (eða tilgreindu annað -march valmöguleikagildi), tengingin þín stage gæti bilað með eða án villuboða. | Gakktu úr skugga um að þú notir sama valmöguleikagildi -march fyrir bæði samantektina með -c skipunarvalkostinum stage og tengja stage. |

| Lýsing | Lausn |

| Með því að beita hls_merge minni eigindinni á fylki sem lýst er yfir innan órúllaðrar eða órúllaðrar lykkju veldur því að afrit af fylkinu sameinast yfir endurtekningarnar í órúlluðu lykkjunni.

|

Forðastu að nota hls_merge minni eigindina í órúlluðum lykkjum.

Ef þú þarft að sameina minningar í órúllaðri lykkju, tilgreinið sérstaklega fylki af gerð fyrir breiddarsamruna, eða lýstu yfir dýpri fylki fyrir dýptarsamruna.

|

| Í aðgerðaminni Viewer hönnunarskýrsla á háu stigi, gætu sumar minningar með virkni birst sem „fjarlægðar“. | Engin.

Þegar a file inniheldur föll sem eru íhlutir og föll sem eru ekki íhlutir, allar breytur með virknisvið eru skráðar í aðgerðaminnislistanum, en aðeins breytur úr íhlutum hafa upplýsingar um þær til að sýna í aðgerðaminni View rúðu. |

| Sumar hönnunarskýrslur á háu stigi mistakast í Microsoft Internet Explorer*. | Notaðu einn af eftirfarandi vöfrum til að view skýrslurnar:

• Google Chrome* • Microsoft Edge* • Mozilla* Firefox* |

| The Loop Viewer í High-Level Design Reports hefur eftirfarandi takmarkanir:

• Hegðun stalllausra klasa er ekki sniðin í lykkjunni Viewer. Síðasta leynd sýnd í Loop Viewer fyrir stall-frjáls þyrping er venjulega svartsýnni (það er hærri) en raunveruleg leynd hönnunar þinnar. Fyrir lýsingu á þyrpingum og báslausum klösum, vísa til Klustun gagnaslóðarinnar í Intel á háu stigi Synthesis Compiler Pro Edition Leiðbeiningar um bestu starfsvenjur. • Stöðvar frá lestri og skrifum úr minni eða prentunaryfirlýsingar eru ekki sniðin. • Mikil endurtekningafjöldi (>1000) veldur hægum afköstum lykkjunnar Viewer. • Þú getur ekki tilgreint endurtekningartalningu sem er núll (0) í lykkjunni Viewer. |

Engin. |

| Tenglar í sumum skýrslum í High-Level Design Reports sem eru búnar til á Windows kerfum virka ekki. | Búðu til hönnunarskýrslur á háu stigi (þ.e. settu saman kóðann þinn) á Linux kerfi. |

| Notkun skipulags af einni ac_int gagnategund í gufuviðmóti sem notar pakka (ihc::usesPackets ) virkar ekki.

Til dæmisample, eftirfarandi kóðabútur virkar ekki:

|

Til að nota þessa samsetningu í hönnun þinni skaltu hlýða eftirfarandi takmörkunum:

• Innri ac_int gagnastærð verður að vera margfeldi af 8 • Gerðaryfirlýsing straumviðmóts verður að tilgreina ihc::bitsPerTákn<8> Til dæmisample, eftirfarandi kóðabútur virkar:

|

| Lýsing | Lausn | |

| Þegar keyrt er uppgerð með mikilli afköst af íhlutnum þínum með því að nota biðröð fallakall, ef þú notar ekki aðgerðina ihc_hls_component_run_all til að keyra íhlutaköllin í biðröð eftir öll ihc_hls_enqueue köllin fyrir þann íhlut, kemur eftirfarandi hegðun fram:

• Í hermi eru aðgerðirnar í biðröð keyrðar. • Í hermi eru aðgerðirnar í biðröð ekki keyrðar, án villu- eða viðvörunarboða. |

Gakktu úr skugga um að þú notir aðgerðina ihc_hls_component_run_all eftir að öll ihc_hls_enqueue kallar á þann íhlut til að keyra aðgerðakall í biðröð. | |

| Ræsir verkefnisaðgerð með ihc::launch_always_run | Til að forðast að fjarlægja fínstillinguna skaltu bæta við smá stund(1) | |

| fjarlægir hagræðingareiginleika sem notaðir eru við verkefnið | lykkja á viðkomandi aðgerð beittu samsvarandi stjórn | |

| virka. | pragma að while(1) lykkjunni í stað fallsins. | |

| Í eftirfarandi kóða tdample, eigindin sem er notuð á fallið er hunsuð. Hönnunarskýrslur á háu stigi sýna II af 1 fyrir þetta verkefni í stað hins umbeðna II af 4. | Eftirfarandi kóði exampLe sýna hvernig þú getur innleitt þessa breytingu fyrir fyrri kóða tdample: | |

|

|

|

| Fyrir Cyclone® V verkefni sem innihalda marga HLS íhluti, þegar þú notar i++ skipunina til að setja verkefnið saman í vélbúnað (i++ -march=CycloneV), gætirðu fengið villu.

Þó að villutextinn sé mismunandi eftir verkefninu þínu, er villuundirskriftin Intel Quartus Prime safnbilun vegna slæmrar setningafræði Verilog. Eining reynir að nota aðgerð sem Intel Quartus Prime þýðandinn finnur ekki. |

Ef þú lendir í þessu vandamáli skaltu setja hvern HLS íhlut í sérstakt verkefni. | |

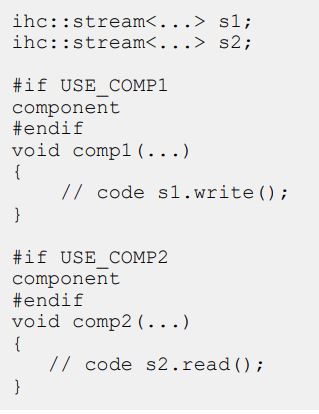

| Að setja saman nokkrar hönnun sem innihalda marga íhluti myndar villu um endurnotkun strauma. | Ef þú lendir í þessu vandamáli skaltu setja saman hvern íhlut í hönnuninni fyrir sig. Þú gætir þurft að bæta fjölvi við kóðann þinn til að gera hvern íhlut kleift að safna saman sérstaklega. | |

| Skoðum eftirfarandi tdample: | ||

|

||

Intel High-Level Synthesis Compiler Pro Edition útgáfuskýrslur

Fyrir nýjustu og fyrri útgáfur þessarar notendahandbókar, sjá Intel HLS Compiler Pro Edition útgáfuskýringar. Ef hugbúnaðarútgáfa er ekki á listanum gilda útgáfuskýringar fyrir fyrri hugbúnaðarútgáfu.

Endurskoðunarsaga skjala fyrir Intel HLS Compiler Pro Edition útgáfu 22.4 útgáfuskýringar

| Skjalaútgáfa | Intel Quartus Prime útgáfa | Breytingar |

| 2022.12.19 | 22.4 | • Upphafleg útgáfa. |

Skjöl / auðlindir

|

Intel High Level Synthesis Compiler Pro Edition [pdfLeiðbeiningar Útgáfa 22.4, útgáfa 23.4, High Level Synthesis Compiler Pro Edition, High Level Synthesis Compiler, Pro Edition |